CBCS SCHEME

ovas tastotate

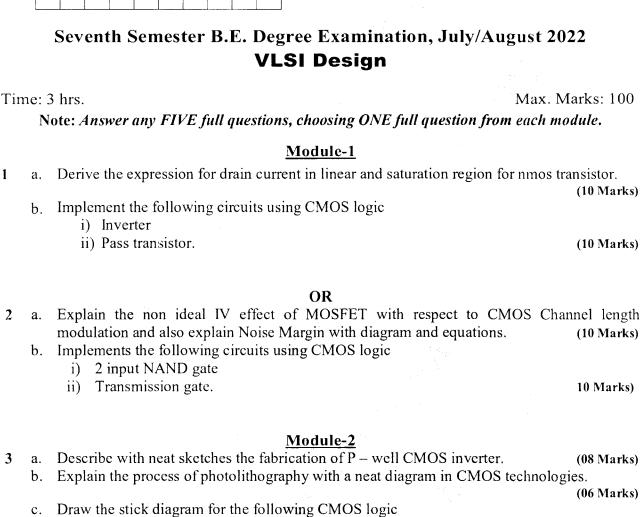

i) Y = A + B + C

ii) 2 input NAND gate.

OR

Explain the layout Design Rules for MOS process with two metal layers. 4 (06 Marks) a.

b. Draw the stick diagram for the CMOS logic Y = (A + B + C)D and estimate the cell area.

(06 Marks) c. Define scaling. Explain the constant voltage scaling and the effect of scaling on device characteristics. (08 Marks)

## Module-3

- Explain with a waveform the propagation Delay, Rise times and Fall Times of a CMOS 5 a. inverter. (08 Marks) Derive the equation of propagation Delay using RC Delay Model for a 1<sup>st</sup> order system. b.

- Compute the Elmore Delay for  $V_{out}$  in the 2<sup>nd</sup> order RC system. (06 Marks) c.

USN

1

2

3

# 18EC72

. ..

(06 Marks)

### OR

- 6 a. Explain Parasitic Delay of common gates in Linear Delay Model. (08 Marks)

- b. Design a circuit to compute F = AB + CD using NAND and NOR by Bubble pushing. (06 Marks)

- c. Calculate the minimum delay in C to compute F = AB + CD using the circuits with NAND and NOR gates and with AOI gates. Each input can present a maximum of 20 $\lambda$  of transistor width. The output must derive a load equivalent to 100 $\lambda$  of transistor width. Choose transistor sizes to achieve this delay. (06 Marks)

#### Module-4

7 a. Explain Resettable Latches and FlipFlops using CMOs transmission Gate. (10 Marks)

b. Explain the Multistage pass transistor logic driven by two non overlapping clocks. (10 Marks)

#### OR

| 8 | a. | Explain conventional CMOs flipflops with neat diagrams. | (10 Marks) |

|---|----|---------------------------------------------------------|------------|

|   | b. | Explain Domino CMOS Logic.                              | (10 Marks) |

#### Module-5

| 9 | a. | Explain the operation of three transistor dynamic RAM cell. | (10 Marks) |

|---|----|-------------------------------------------------------------|------------|

|   | b. |                                                             | (10 Marks) |

#### OR

a. Write short notes on :

10

|    | i) Built in Self Test (BIST)                                       |            |

|----|--------------------------------------------------------------------|------------|

|    | ii) Scan Design Technology                                         | (10 Marks) |

| b. | Explain briefly logic verification principle with a block diagram. | (10 Marks) |

\* \* \* \* \*